The Gate Array News 2025.

It’s July again, and a new season is coming to an end. During this period, we’ve explored a range of topics on the blog: from how to implement electrical models on FPGAs—even on very small ones—to optimizing Speedgoat models using the fixed-point solver.

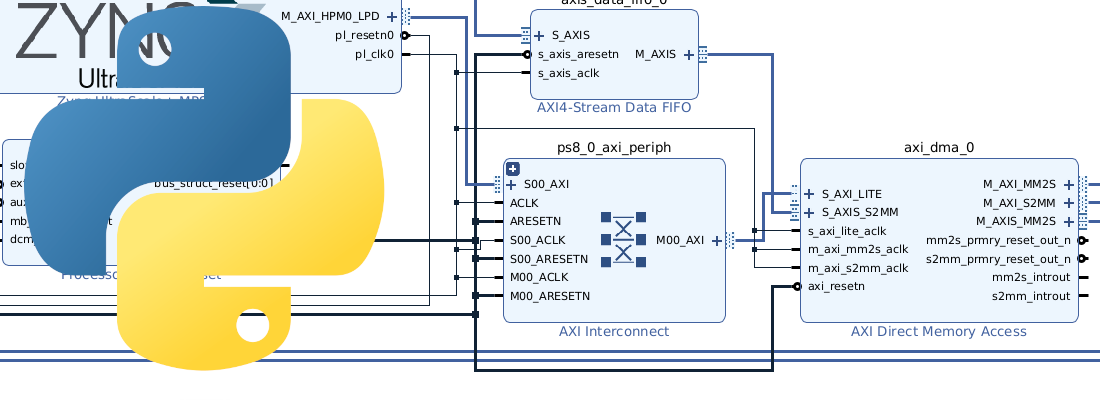

A special focus this season was on moving data within the FPGA or SoC using Python, which I covered in several articles. I also acquired a new development board from eBay!

In recent months, I began publishing content about implementing cryptography algorithms on FPGA—a topic that will continue to be important in the coming months.

Outside of ControlPaths, there were also several exciting stories in the FPGA world worth highlighting.

As usual, in this last article of the season, we’ll take a moment to review some of them.

FPGAs are in their 40s!

The most important one, FPGA turn 40! The first FPGA was designed by Xilinx on 1985, the XC2064.

This device was built using 2 µm technology and features 64 CLBs arranged in an 8×8 matrix. With up to 58 I/O pins and a maximum frequency of 10 MHz, it was truly revolutionary. For the first time, not only the software—but also the hardware—could be changed after manufacturing.

To design for this device, Xilinx released XACT, the predecessor to what would later become Xilinx ISE.

When I talk about FPGAs at cybersecurity or general technology conferences, I’m often asked whether FPGAs are a mature technology. The answer is clear: absolutely. In fact, they’re currently at their peak.

Forty is the new twenty!

Spartan7 Ultrascale+ release.

After some waiting time, AMD finally released the first devices of the newest cost-optimized portfolio, the Spartan7 Ultrascale+. Maintaining multiple manufacturing lines is something every company tries to acvoid, and for AMD is exactly the same. Today, we can find in its portfolio families with 28nm, 20nm and 16nm, and this just for FPGA. If we include SOC devices, the liast spands furher to 10nm and 7nm for Versal series. With the introduction of Spartan Ultrascale+, AMD completed its cost-optimized line up on the 16nm technology.

last year I didn’t see the need of this new family, but now is clear that the goal was to consolidate the 16nm portfolio.

During the AMD Tech Day, the team presented some features of this devices, especially focused on cybersecurity, and they were very interesting.

For now, there is only one development board, the SCU35, but it is not announced yet, so we need to wait a bit more to have one.

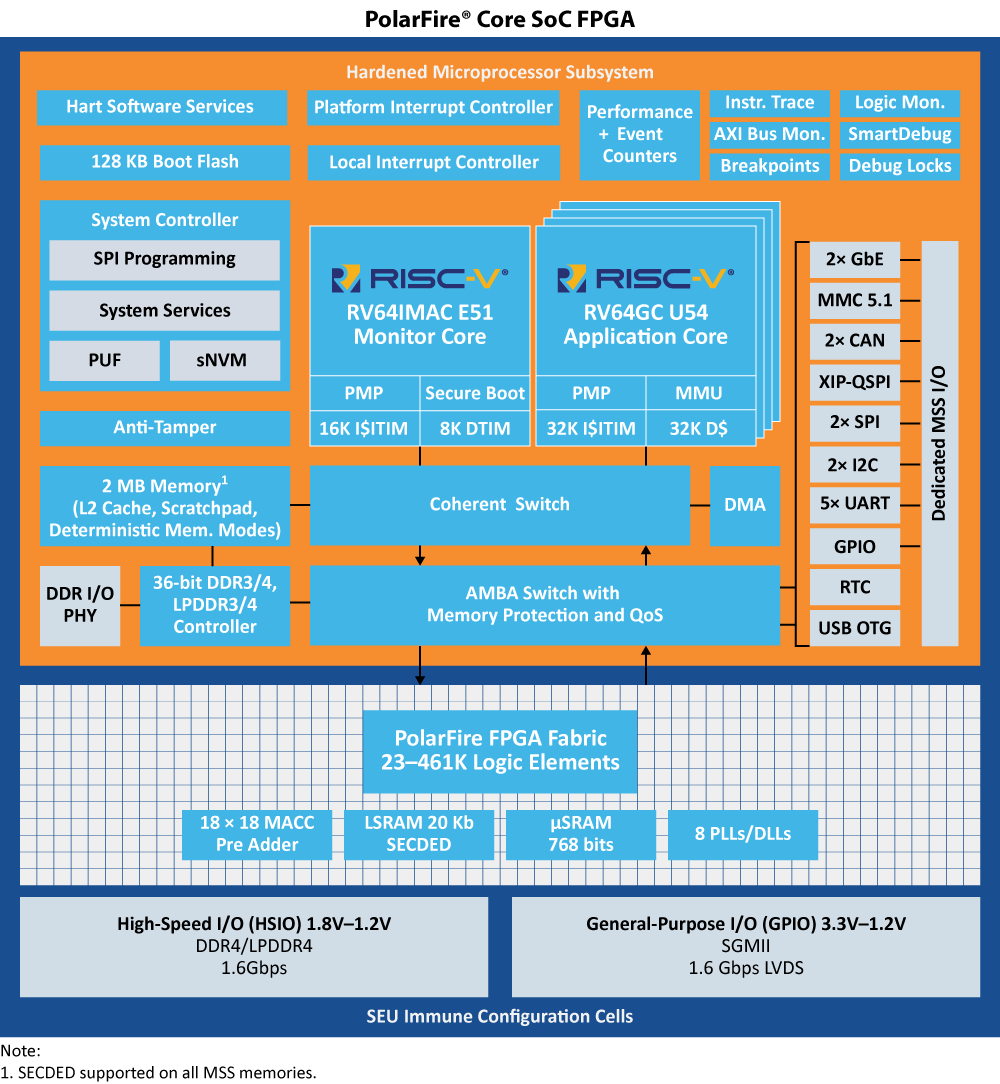

Microchip PolarFire Core announcement.

This year, Microchip finally announced the new family of FPGA, the new PolarFire 2!, oh wait, no, it is the PolarFire Core FPGA and SOCs. While PolarFire 2 would come with an extra of power, resources and speed, Microchip decided finally release a cost-optimized version, the PolarFire Core FPGAs and SoCs.

On the description of this new devices, the word cost is very present, so it is clear the goal with this device. And it is a very good movement from Microchip, since the cost of PolarFire devices is high in comparision with other platforms.

The reason behind the cost is simple: these devices are not cheap to manufacture due to their internal architecture and the features required for aerospace and defense applications.

However, around 90% of FPGA applications operate at sea level, where the risk of Single Event Upsets (SEUs) is minimal. In these environments, it’s entirely feasible — and much more affordable — to simply add an encrypted flash memory to store the bitstream securely.

On the other side, from my point of view, Libero is a big “but” if you are planing to migrate to Microchip FPGAs. I know that they are working in a new IDE, but it is going slow.

Altera - Intel separation, who will keep the kids?

Things have change a lot in Altera this last months. In march I was attending the Embedded World Conference, and one of the keynotes was given by Sandra Rivera, CEO of Altera on that moment, that was part of Intel. Now there is no Sandra Rivera, and there is no Intel.

On April, Intel sold a big part of Altera to the investment group Silver Lake for $8.75 Bilions. A great deal since Intel acquired Altera in 2015 for $16.7 Bilions. Seems that every thing is turning more cheaper except houses.

What you are going to read from here, is my opinion.

While AMD was able to integrate FPGA and SOCs, and now they are releasing products mixing these two technologies, for Intel, Altera, and FPGAs always were a different business. I was very excited when Intels adquired Altera because I though on new Xeon devices with integrated FPGAs, something like a SOC, but using a Xeon instead of an ARM. The reality is that it never happened.

Playing a big imagination game, let’s imagine a device like this, does not matter if the processor is a Core i7 or a Ryzen 7, a high-end microprocessor with a 500k CLB FPGA. Now, having functions to configure and manage the FPGA, like FPGA Manager or XRT, software developers will be able of, not only use the resources of the processor, but also include in the software its own HW accelerator, and be able of using it to improve the performance. Imagine the new Grand Thef Auto 7 (with FPGA accelerators).

This is the way how I imagine the future of FPGA.

FPGA projects

Also, during this seasoin I found two interesting FPGA projects related to the FPGA world.

New FPGA-based console, the SuperStation one

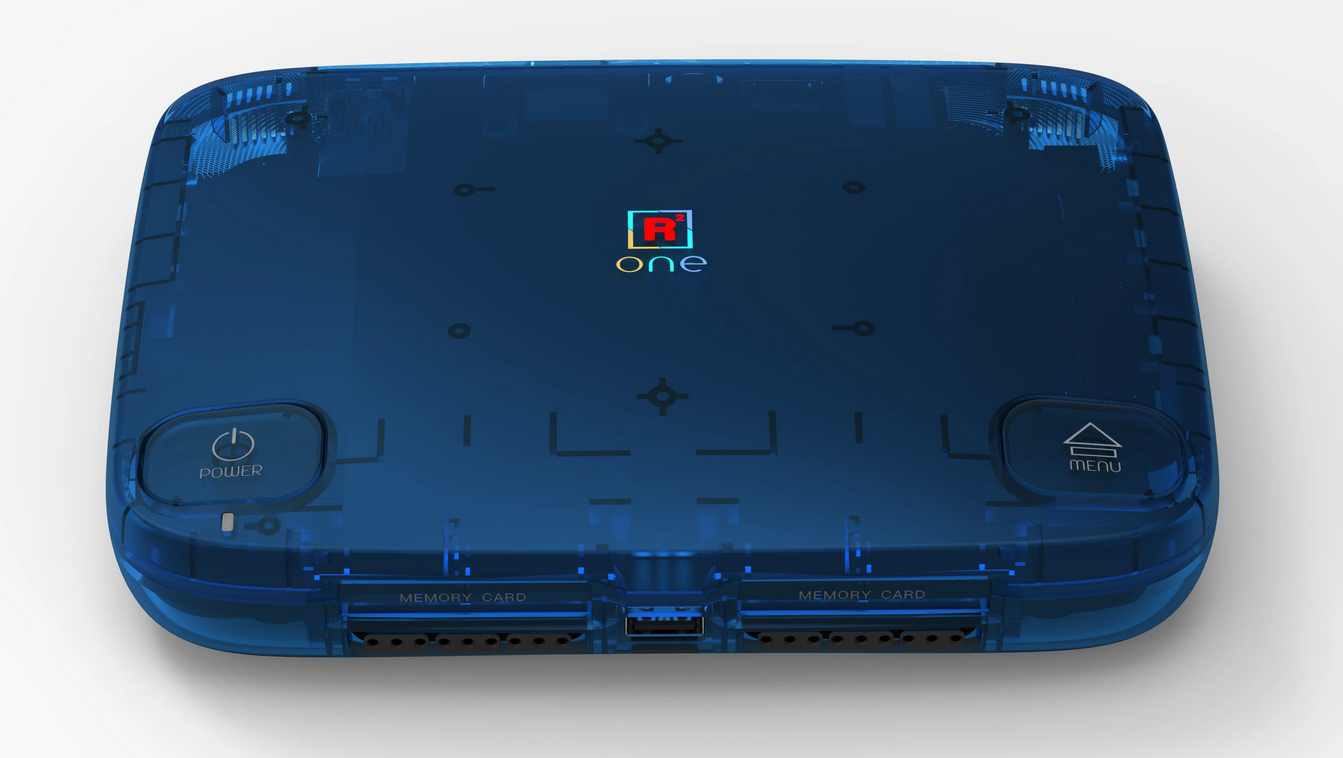

After the flop of the SuperSega console, the team at RetroRemake has developed a new console based on FPGA technology, the SuperStation One, a PlayStation-inspired system powered by a Cyclone V FPGA.

This open-source console supports original PlayStation controllers and even memory cards. While it was originally designed to run PS1 games, its hardware is fully compatible with the MiSTer FPGA platform. Available in various colors, the SuperStation One might just be the perfect retro gift for this Christmas!

The eFPGA from Zeroasic platypus

ARM does not sell microprocessors but IP cores to integrate in your own chip. This exactly can be done with FPGA, sell the IP of the FPGA, and let the manufacturers to integrate it in their new devices. This is known as Embedded FPGAs or eFPGA.

The team of Zeroasic has released the Platypus family, an open FPGA architecture ready to be included in your new IC design. Not only the architecture is open, but also the bitstream generated and the development tools.

The version 0.1.0 of the architecture was released on March 18 with four different flavours, each with different number of resources.

controlpaths.com new look!

And finally, if this isn’t your first time visiting the blog, you may have noticed that something has changed at ControlPaths.

I’ve updated the interface to make it more user-friendly and professional. At the top of the page, you’ll now find a Subscribe button. Since I’m strongly committed to privacy, this blog does not collect any personal data — which also means I have no visibility into who my audience is, or even how many real visits I receive. The idea behind the subscription is to get to know you better and to share extra content through a newsletter. The only information you’ll need to provide to my email marketing provider is your email address — no name, no country, no additional data. And of course, you can unsubscribe from the newsletter at any time.

But that’s not the only news on the blog. Starting in October, I’ll be launching ControlPaths Academy, a new platform offering courses related to FPGAs and SoCs, available in both English and Spanish. The first course will be released in October.

Additionally, if you need training or support with your FPGA or SoC projects, feel free to reach out via email as always.

That wraps up this season. During August, I’ll be working on finalizing the website and preparing the course platform to be ready by September.

f you’re attending DEF CON in Las Vegas, I’ll be speaking at the Creators Stage about privacy, cryptography, and FPGAs.

See you in September!