FPGA Conference 2024

This week I have been in Munich for the FPGA Conference Europe. This event is based on a set of conferences separated in six different tracks. In addition, there is a showroom where you can find different booths where they show new products and demos. In this article, I am going to tell you what I have found in this year’s edition.

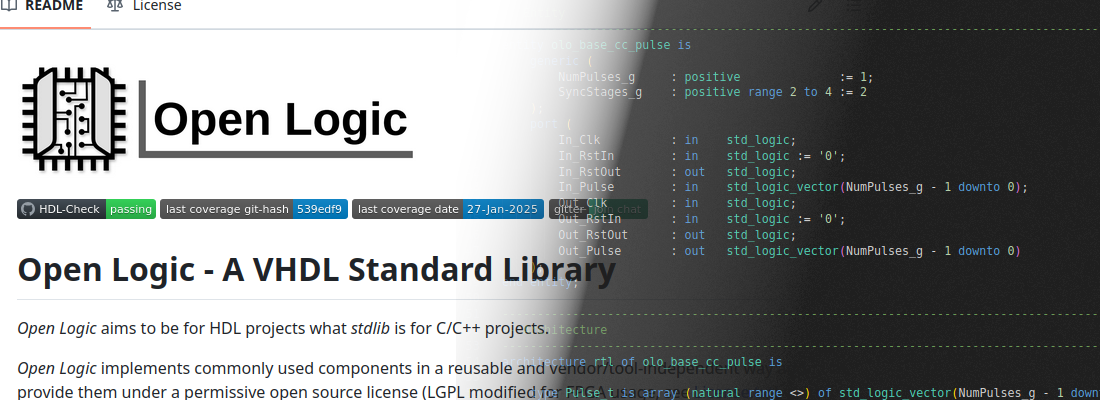

One of my goals with this visit was to verify if the way we are working is the correct way, I mean, usually, I start using different tools like Sphinx, Markdown and RST for documentation, or Icarus for simulations, but I am not pretty sure if there is another way to do it more efficiently. I was surprised that one of the talks about HDL documentation given by PLC2 uses the same tools as we use. Also, they have the same problem as us, the documentation of the VHDL/Verilog code, being the custom tools preferred by them. Also talking with other visitors that also have created custom tools for that purpose. When I say custom tools, I am talking about tools that mix custom parsers and third-party tools like Yosys.

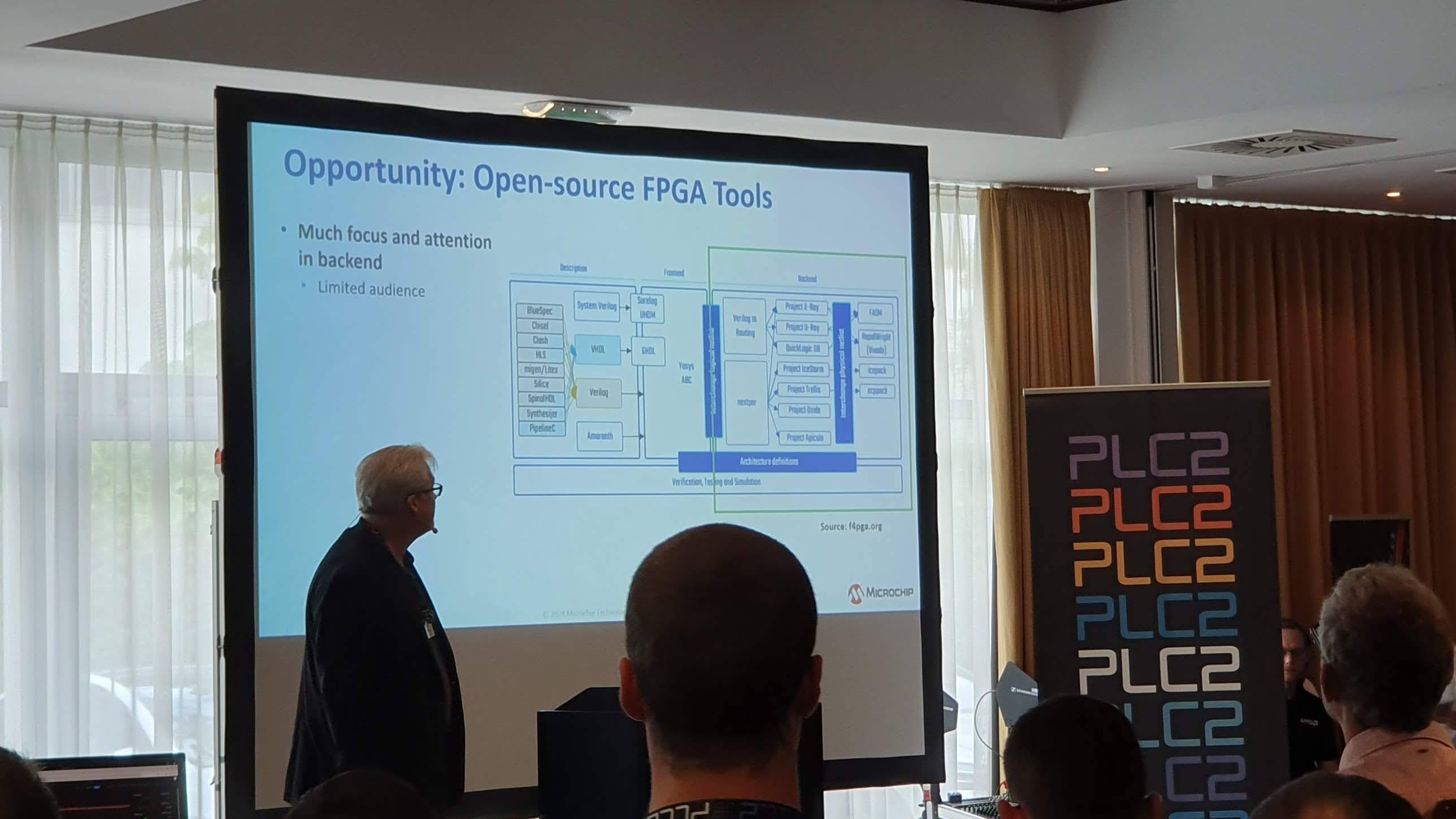

Regarding the simulation, almost everybody uses Questa and Modelsim, instead of open-source tools like Icarus, which is the selected tool by us. The fact that is free and its speed makes Icarus for me very interesting. Open-source tools had one talk given by Arrow, which was disappointing. The speaker just read the slides with information without diving into how to create a project, the differences between them… however, open-source tools played a leading role in the Microchip’s keynote.

On the keynote they revealed that they are interested just in the documentation side, but not in the implementation one. This is a little step into the open-source tools, but is a step after all, which is very good.

Enclustra gives an interesting talk about fixed-point in FPGA, presenting a tool developed by them that makes easy fixed-point operations. The tool is based on a Python script and a VHDL library, so you don’t need to think about the bit extensions in multiplications for example, since using their functions all must work correctly. Also, the tool is designed thinking in the DSP Slice, so it will use them in a smart way. This is one tool that deserves an article soon.

Almost all the talks were very interesting but one of them was by far my favorite. The talk’s title was All FPGA are equal, but some FPGA are more equal. This simple title hides an interesting talk about the efficiency of LUT6 vs LUT4, the difference in speed of the FPGA from different vendors, the differences in the internal structure of different FPGA. regarding the topic of the talk, it was a very funny talk, and also very interesting. The talk was given by Dirk Koch, who also talked about malware on FPGA, yes, like a virus in your computer. A part of his job can be found on the webpage of the [Novel Computing Technologies of Heilderberg University.

Finally, last day, Jim Lewis gave a talk about OSVMM, a verifying toolbox for VHDL. The tool is amazing allowing even link tests with requirements, which is very interesting for projects that use Jira or Redmine. The bad side is that it is only supported by VHDL but fortunately, a Verilog tools exist, UVM, so is time to start working with it.

The conference finishes with Adam Taylor, from Adiuvo Engineering, with a talk about Petalinux, and all the steps to create a Petalinux distribution as well as the design of a driver for the ZU Board temperature sensors.

To summarize, the FPGA Conference is an event for all the FPGA developers. Embedded World has also very good conferences, but it just has one track for FPGA/SoC, while here you have six different tracks all about FPGA. In addition, all the attendees are related in some way to FPGA, so it is very easy to start a conversation with them, and exchanges working methodologies or issues.